最近一直在挖先进封装的瓜,发现现在半导体圈里聊得火热的CoWoS、CoPoS、FOPLP这些词,好多朋友听完都一头雾水:不就是装芯片吗?怎么还能决定AI发展的节奏?

就和大家一起掰扯清楚下一代封装技术的核心——CoPoS,还有它和现在火得一塌糊涂的FOPLP到底有啥关系,为什么说它才是未来AI算力降价、普及的关键。

先聊点背景,现在的高端AI芯片,为什么造不出来也买不起?

你肯定听说过英伟达的H100、B200显卡,一块就几十万,有钱还不一定能买到。

为什么?除了芯片本身难造,更卡脖子的其实是封装环节。

现在高端AI芯片不是一块单独的GPU,得把计算核心、十几颗HBM高带宽显存还有其他组件拼在一起,就像把十几台高速服务器塞到一个巴掌大的盒子里,还要保证它们之间的数据传输零延迟、不会过热死机。

之前台积电解决这个问题的技术叫CoWoS,简单说就是把这些芯片都放在一片圆形的硅晶圆上,通过硅中介层把它们连起来。

这个技术牛是真牛,但问题也很致命:

浪费太多:圆形晶圆边缘没法放芯片,面积利用率只有45%左右,造10块有5块的地方都浪费了,成本能不高吗?

产能上不去:12寸的晶圆最多也就放十几颗大AI芯片,就算台积电把产能拉满,一年也造不出多少,巨头们抢产能都抢破头了。

上限快到顶:芯片越做越大,晶圆就那么大,散热、翘曲的问题越来越难解决,再往下走物理瓶颈就在那摆着。

CoPoS到底是啥?一场“化圆为方”的生产革命

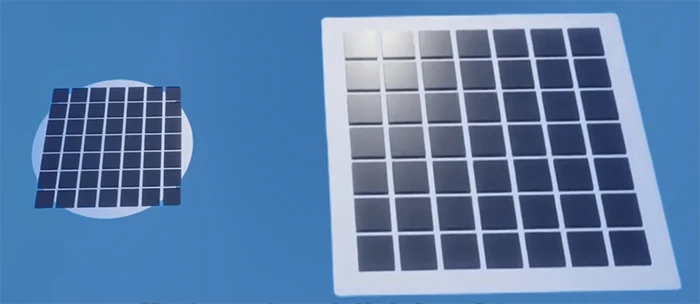

其实台积电早就看到这个问题,所以憋了个大招:CoPoS,全称叫Chip-on-Panel-on-Substrate,你不用记这个名字,只要记住它的核心逻辑:把原来放芯片的圆形晶圆,换成了方形的大面板。

你可以这么理解:原来我们是在圆形的餐桌上摆菜,边角的地方摆不下都浪费了;现在换成了超大的方形餐桌,能摆的菜翻了好几倍,一点空间都不浪费。

这个改变听起来简单,其实是从根上改了封装的逻辑:

面积利用率直接从45%拉到95%以上,单块面板的面积是12寸晶圆的3-8倍,一次能造的AI芯片直接翻好几倍,产能问题一下就解决了大半。

材料也换了,原来的硅中介层换成了玻璃或者蓝宝石,热稳定性更好,芯片做大了也不会弯,散热效率更高,再也不用担心大芯片过热出问题。

单位封装成本直接降10%-30%,以后AI芯片说不定真的能从几十万一块,降到普通人也能摸得到的价格。

同样是方面板,CoPoS和现在火的FOPLP有啥不一样?

FOPLP(扇出型面板级封装),和CoPoS一样都是用方形面板,好多人把它们搞混。其实它们俩的定位完全不一样,是互补的关系,不是竞争:

简单说就是:

FOPLP负责把中低端芯片的成本打下来,让汽车、手机、智能家居的芯片更便宜;

CoPoS负责解决高端AI算力的产能问题,让大模型训练、超级计算机的算力不再卡脖子。

而且台积电现在的思路很明确:CoPoS其实就是把FOPLP的面板工艺和原来CoWoS的中介层优势结合起来,相当于站在FOPLP的肩膀上,专门给高端场景做的定制版。

未来格局:并存,而非取代

这一轮封装技术的革命,本质上就是把AI算力的“生产成本”打下来:

之前只有大厂能用得起的AI算力,未来会因为封装成本的下降,逐步落到普通人的手机、汽车、智能家居里,这才是技术迭代真正的价值。

当前先进封装是后摩尔时代突破芯片性能天花板、实现“异质集成、算力跃升”的核心技术路径,CoWoS、FoPLP与CoPoS正是先进封装产业不同技术路线、不同应用层级的核心代表性成果,共同构成了先进封装产业向更高集成度、更广覆盖场景迭代的核心支撑。

CoPoS则是先进封装面向中高端场景性能与成本平衡的核心探索方向,作为下一代2.5D封装的迭代方案,它填补了高端与普惠级先进封装之间的技术空白,代表了先进封装未来面向中高端AI推理、中端算力芯片等场景的演进路线。半导体行业的竞争,正在从“制程战”转向“封装战”。当摩尔定律逼近物理极限,晶体管微缩的边际效益递减,封装不再是芯片制造的最后一公里,而是决定性能、成本与交付的第一战场。谁能在封装上建立优势,谁就握住了算力时代的命门。通往AI未来的路,或许不是更小的晶体管,而是更大的面板。

文章转发请备注出处:https://www.hotchip.com.cn/ccdcxj/

阅读推荐