一、后摩尔时代的成本挑战

在后摩尔时代,半导体工艺演进仍在持续,但其经济效益的”黄金定律”正遭遇前所未有的挑战。传统单片系统级芯片(Monolithic SoC)在向7nm及以下工艺节点推进时,面临着成本急剧攀升的困境。这一”成本墙”主要由两大关键因素构成:

非重复性工程成本增长:在先进制程节点下,芯片设计的非重复性工程成本呈现爆发式增长。以5nm工艺节点为例,单颗SoC的设计成本已攀升至4亿美元量级,相较之下,28nm节点的设计成本仍维持在5000万美元左右的水平。这种成本增长曲线使得只有具备海量出货量的旗舰产品才能承担相应的研发投入。

良率瓶颈日益凸显:随着芯片尺寸的增大和工艺节点的演进,晶圆缺陷对良率的影响愈发显著。实测数据表明,在5nm工艺节点下,面积达到800mm²的大尺寸SoC中,由缺陷导致的额外成本占比可能超过总制造成本的50%,这直接推高了有效芯片的单位成本。

在半导体行业面临严峻成本挑战的背景下,亟需一种能够打破性能与成本线性增长关系的新型解决方案。Chiplet技术的出现并非单纯的技术升级,而是代表着从”集成”(Integration)到”分解”(Disaggregation)的根本性设计理念变革。该技术通过将复杂的SoC系统拆分为多个功能独立且物理隔离的小型芯片单元(即Chiplet),再借助先进封装工艺实现系统级重构。

这一技术变革的核心驱动力,其意义远不止于高性能计算领域对顶尖算力的追求。更具突破性的是,它为对成本高度敏感的应用场景开辟了一条突破传统成本限制的创新路径。

二、核心技术剖析

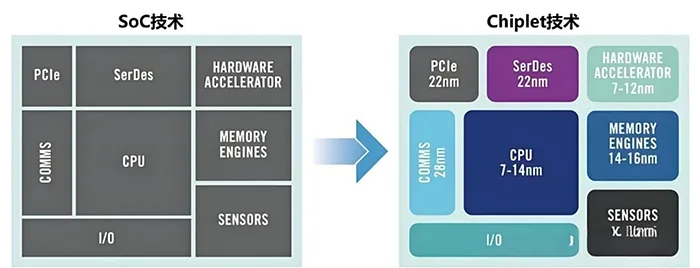

架构对比:从单片(Monolithic)到多片(Multi-Die)的根本性转变

传统SoC架构:采用”集中式”设计模式。所有功能模块,包括数字逻辑、模拟电路、射频和I/O接口等,都被强制集成在单一硅片上,并统一采用最先进的工艺节点制造。这种架构下,各模块形成紧密的绑定关系。

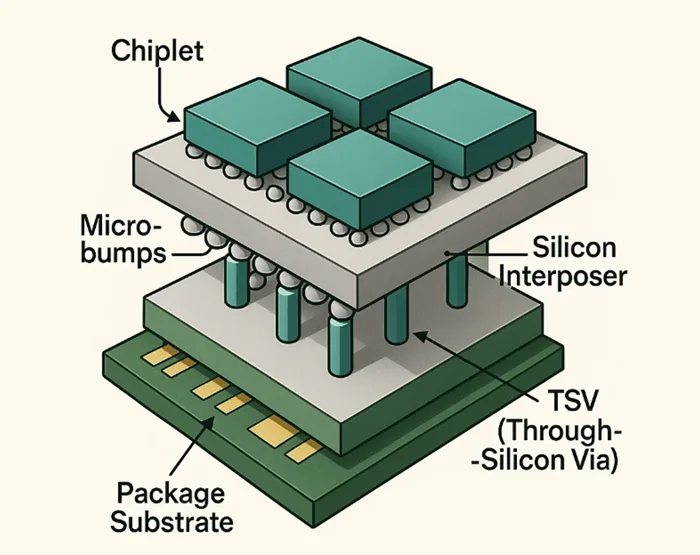

Chiplet架构:采用”分布式”设计理念。它将SoC的功能模块分解为独立的芯粒单元,每个芯粒都是一个独立的物理实体。这些芯粒可以分别进行设计和制造,最终通过2.5D/3D、Fan-Out等先进封装技术实现互连,构建成完整的系统级封装(SiP)。

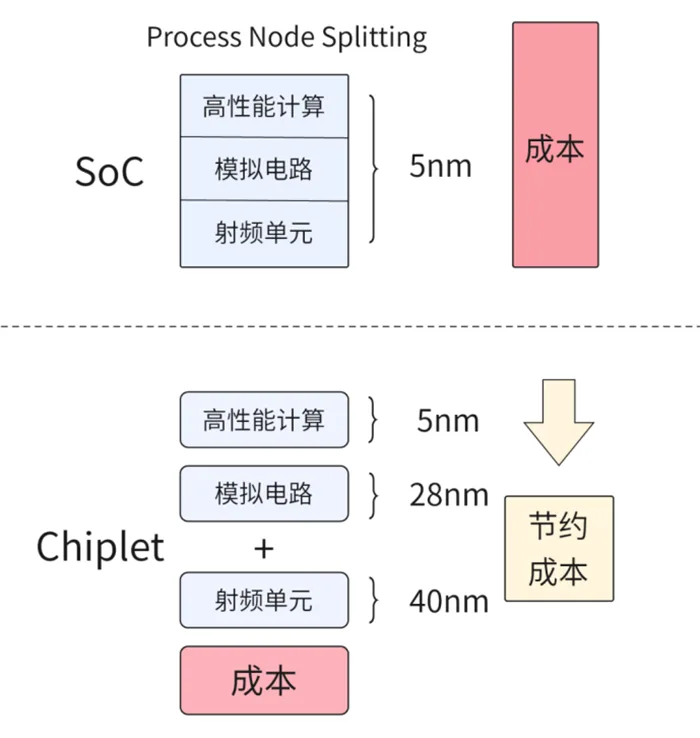

工艺节点分拆 (Process Node Splitting) — 良率与成本的最佳匹配

传统SoC架构面临的主要制约在于其”统一工艺”的局限性。所有功能模块不论性能需求差异,都被强制采用单一且通常是最先进的工艺节点,这不仅造成资源浪费,更带来显著的良率风险。Chiplet技术从根本上突破了这一限制,实现了”功能适配工艺”(the right process for the right function)的设计理念。

1、异构工艺的经济学:不同功能模块对工艺制程的需求存在显著差异。

(1)计算密集型模块(CPU核心、AI加速器等):

• 核心优势:充分利用先进工艺(7nm/5nm)的高晶体管密度特性

• 关键收益:实现更低的功耗和更高的工作频率

• 必要性:达成性能指标的关键技术保障

(2)模拟/I/O/射频模块:

• 核心需求:电压稳定性、噪声抑制和信号线性度等特性

• 工艺适配:28nm/40nm等成熟制程即可满足性能要求

• 成本优势:显著降低实现成本同时保证可靠性

• 风险规避:避免先进工艺可能带来的漏电流和噪声干扰等问题

2、规避良率风险与掩膜版成本:将全部功能集成于单一大型SoC芯片,并采用先进制程工艺,存在显著风险。

(1)良率控制:大尺寸芯片在先进制程下良率急剧下降。采用Chiplet方案可将核心计算单元保持先进工艺的同时缩小芯片面积,显著提升这部分高价值模块的良率。其余I/O和模拟模块则可转移到良率更高的成熟工艺,从系统层面解决良率问题

(2)成本优化:先进工艺掩膜版成本高达数百万至上千万美元。工艺节点分离后,仅核心计算Chiplet需要承担高额掩膜费用,而占比较大的I/O和模拟Chiplet可采用成本更低的成熟工艺掩膜版,实现源头上的成本控制。

模块复用 (Die Reuse) — NRE成本的摊薄器

在传统SoC设计中,IP核(包括PCIe控制器、USB接口等)通常以软核或固核形式存在。每当这些IP核被集成到新的SoC时,都必须重新经历完整的前后端设计流程,包括集成验证和物理版图的布局布线。这一过程不仅耗费大量时间精力,而且每次集成都需要承担相应的NRE成本。而Chiplet技术彻底改变了这一传统模式。

1、从软件IP到硬件IP的转变

Chiplet将功能IP转化为可直接复用的物理硬核——即经过完整设计、制造和测试验证的独立裸片(Die),相当于构建了一个“硅片级IP库”。在设计新产品时,工程师无需从逻辑代码开始集成,而是可以直接选用现成的标准化Chiplet,如同在电路板上选用标准元器件。

2、跨产品线分摊高额NRE

模块复用的核心经济价值在于NRE成本的摊销。一颗高研发投入的通用I/O Chiplet或射频Chiplet,一旦完成流片验证,其高昂的NRE成本(包括设计、验证和掩膜版费用)便可通过在不同产品线和客户项目中的复用持续摊薄。

例如,企业可开发一款集成多种标准接口的I/O Chiplet,并将其应用于从低端到高端的整个MCU产品家族。这样,原本需要为每个MCU型号单独承担的接口设计与验证成本,就能分摊至整个产品线的销量,大幅降低单款产品的研发门槛。

3、缩短上市周期与推动开放生态

(1)加速产品上市(TTM):复用模式使企业能集中研发资源于核心差异化功能(如专有算法加速器),而通用模块则采用成熟的Chiplet方案。这种“核心自研+通用外购/复用”模式显著缩短了设计到量产的周期。

- 促进开放生态:模块复用是构建开放Chiplet生态(如UCIe联盟推动的市场)的基础。未来,芯片设计公司可像采购软件一样选购标准化第三方Chiplet,从而推动半导体产业的协作与创新。

封装与测试协同——成本优化的关键支撑

若将模块复用和工艺分拆视为Chiplet的核心理念(“道”),先进封装与协同测试则是实现这一理念的技术手段(“术”)。尽管先进封装(如2.5D/3D)确实增加部分成本,但它更是实现前两大优势的必要支撑。此外,与测试策略的协同进一步带来了系统级成本优化。

1、”已知良好裸片”( KGD)策略

这是Chiplet成本控制中一个关键但常被忽视的环节。其核心理念在于:在最终封装集成前,确保每一颗独立的Chiplet都具备完整功能并符合性能标准。

| 对比维度 | 传统单片SoC测试 | Chiplet KGD测试策略 |

| 测试对象 | 一颗巨大的、高集成度、高价值的单片Soc | 多个小尺寸、功能相对单一、低成本的独立Chiplet |

| 成本影响分析 | 测试大而复杂的系统,成本高 | 测试小而简单的单元,容易快捷,测试成本更低 |

| 缺陷定位 | 难以精确快速定位;一旦发现关键缺陷,整颗昂贵的SoC只能报废 | 缺陷可被精准隔离到某一颗具体的Chiplet上,避免“一颗老鼠屎坏了一锅粥” |

| 报废成本 | 报废的是一颗包含了所有功能模块和完整制造流程的SoC | 报废的仅仅是一颗功能单一的小Chiplet,其价值远低于最终的SiP成品 |

| 高品 | 极低 | 封装前剔除所有不良裸片,确保进入高价值封装环节的都是“好料” |

| 最终良率 | 最终系统良率=晶圆制造良率x封装良率 | 通过KGD策略,最终系统良率=(KGD1良率xKGD2良率x…)x封装良率,将复杂系统良率分解为多个独立可控的Chiplet良率问题,显著提升最终系统良率并减少浪费与返工成本 |

因此,尽管先进封装本身带来额外成本,但其支撑的KGD测试策略通过大幅提升系统级良率、减少高价值材料浪费,最终创造了远超封装成本的经济效益。这种与测试的深度协同,正是Chiplet实现成本优化的关键所在。

三、具体应用场景分析

TWS耳机:功耗、体积与成本的极致平衡

TWS耳机作为对成本、功耗和尺寸高度敏感的产品,传统SoC方案需要在单芯片上集成射频、音频编解码、数字控制和电源管理等模块,这种”全集成”设计在工艺选择和成本控制上存在明显局限。

1、成本优化方案:异构工艺的极致应用

Chiplet技术为TWS芯片提供了理想的优化方案,其关键在于工艺节点的精细化拆分:

(1)工艺拆分:

• 射频前端 (RF Front-End):采用成熟且低成本的RF SOI或55/40nm RFCMOS工艺,满足噪声和线性度要求。

• 音频编解码器 (Audio Codec):选用40nm或更成熟的模拟工艺,确保低噪声和高精度。

• 主控MCU与DSP单元:采用28nm或22nm ULP工艺,满足高性能和低功耗需求。

(2)模块复用:

标准化蓝牙射频和音频编解码Chiplet可复用在不同档次产品中,显著降低NRE成本。

(3)封装与测试协同:

采用KGD独立测试提升良率,结合FOWLP或高密度SiP技术实现微型化封装。

电源管理芯片(PMIC):灵活性与可靠性的最佳平衡

现代PMIC需要集成多路电源轨和复杂数字控制逻辑,传统单片SoC方案难以同时满足高压大电流模拟电路和低压精密数字电路的工艺需求。

2、成本优化方案:标准化模块的灵活组合

Chiplet技术通过模块复用实现快速产品迭代和定制化开发:

• 模块复用:将Buck、Boost、LDO等功率模块设计为标准功率Chiplet,搭配统一控制Chiplet,大幅缩短开发周期。

• 工艺分拆:功率Chiplet采用成熟BCD工艺,控制Chiplet选用40nm或28nm CMOS工艺。

车载MCU:安全、迭代与成本的三重平衡

汽车电子对芯片的功能安全、可靠性和长期供应有着极其严格的要求。Chiplet技术为应对这些挑战提供了创新解决方案。

1、成本优化方案:安全认证成本的锁定与复用

Chiplet在汽车领域的关键价值在于通过模块复用显著降低功能安全认证成本:

• 模块复用:

开发通过ASIL-D认证的”安全岛”Chiplet,产品升级时仅需更换应用处理Chiplet,避免全芯片重新认证。

• 工艺拆分:

• 应用处理Chiplet采用16/7nm等先进工艺

• 安全岛和I/O Chiplet使用40nm或28nm车规级工艺

接口芯片:专业分工的最优解

高速接口芯片的物理层(PHY)是典型的模拟电路设计,而控制器则是纯数字逻辑,传统SoC集成面临巨大挑战。

1、成本优化方案:IP硬核化与市场化

Chiplet推动IP商业模式从软核授权转向实体硬核:

• 工艺拆分与模块复用:

专业IP厂商可将高性能PHY开发为独立Chiplet,采用最优工艺。SoC厂商可直接采购已验证的PHY Chiplet(KGD),与主逻辑Chiplet集成。

显示驱动芯片:破解大尺寸面板成本困局

大尺寸高分辨率面板需要多颗驱动IC协同工作,其内部高压驱动与低压逻辑(TCON)存在工艺冲突。

1、成本优化方案:逻辑与驱动的分离

Chiplet技术有效解决DDIC成本难题:

• 工艺拆分:

• 高压驱动采用成熟HV工艺

• TCON逻辑采用28nm等先进低压工艺Chiplet

• 模块复用与封装协同:

同一TCON Chiplet可搭配不同数量的标准化驱动Chiplet,灵活适配各类面板规格。

三、挑战与未来发展趋势

当前面临的核心挑战

1. 标准化困境:互联接口的碎片化问题:Die-to-Die互联标准不统一成为生态发展的主要障碍,UCIe标准的普及程度将直接影响开放Chiplet生态的发展。

2. 设计工具链的转型挑战:现有EDA工具主要面向单片SoC设计,在多Die协同设计、热管理和多物理场仿真方面仍存在明显不足。

3. 供应链与商业模式的构建难题:Chiplet产业面临责任界定、利润分配等商业问题,同时需要建立可靠的KGD保障体系和深度供应链协同机制。

4. 成本平衡的新考量:2.5D/3D先进封装技术和异构集成测试带来新的成本因素,需要与硅片成本节省进行综合权衡。

未来发展趋势

1. 技术发展方向:混合键合技术、AI驱动的EDA工具以及光电共封装等创新技术将持续推动产业进步。

2. 应用场景拓展:Chiplet技术将深入边缘计算、物联网、消费电子定制化和汽车电子升级等领域,实现真正的模块化配置。

四、结论

随着摩尔定律经济效益逐渐减弱,传统单片SoC面临日益严峻的成本挑战,半导体产业正在经历一场根本性的范式转变。本文系统性地阐述了以成本优化为导向的Chiplet技术,它不仅在高性能计算领域具有前沿价值,更是解决各类应用市场成本困境的核心战略。

Chiplet技术的本质在于对传统SoC的”解构”与”重构”,通过三大核心手段重塑芯片成本结构与商业模式:

• 模块复用将IP从一次性软件授权转变为可重复使用的硬件实体,大幅摊薄NRE成本,显著降低创新门槛。

• 工艺分拆突破单一工艺限制,为每个功能模块匹配最具性价比的制造工艺,实现系统级成本与性能优化。

• 封装与测试协同,特别是KGD策略,将复杂系统良率问题分解为可控单元问题,最大限度减少物料浪费,确保产品商业可行性。

展望未来,Chiplet技术发展已超越单纯的技术演进,正在推动形成更加开放、协同、专业化的产业新生态。从设计方法、EDA工具到IP商业模式和供应链关系,整个半导体价值链都将围绕Chiplet进行重构。这不仅是一场技术革命,更是半导体产业协作模式的深刻变革。在这场变革中,率先拥抱开放标准、构建强大生态系统的企业,将在后摩尔时代掌握定义产业格局的主动权。

Chiplet的时代,已经来临!