在半导体行业跨越半个多世纪的发展史诗中,“摩尔定律”——即集成电路上可容纳的晶体管数目约每隔18-24个月便会增加一倍——犹如一盏始终照亮前路的明灯,指引着产业向着制程微缩的单一方向狂奔。然而,当晶体管的尺寸逼近物理极限(如原子尺度的量子隧穿效应),当一座先进晶圆厂的建造成本飙升到数百亿美元,这条曾经笃定的道路正变得日益崎岖与昂贵。业界共识已然形成:单纯依靠制程微缩(More Moore)来提升芯片性能与功能的时代,正在缓缓落幕。

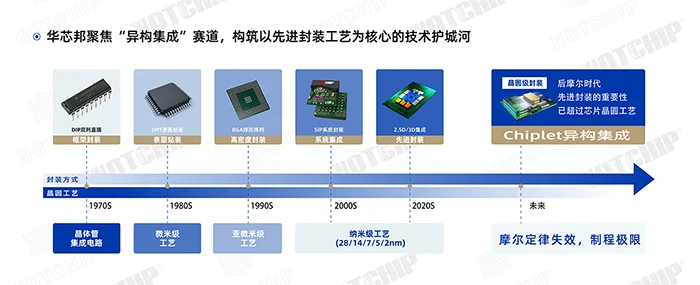

那么,未来的道路在何方?答案正从芯片的“外部”与“整体”中浮现——先进封装与异构集成。这不再是关于如何将晶体管做得更小,而是关于如何将不同工艺、不同功能、甚至不同材料的“芯片单元”,像搭建乐高积木一样,以最优的方式集成在一起,形成一个更强大的系统。华芯邦科技,敏锐地洞察了这一历史性转折,并将其明确为公司的战略愿景:“成为全球数模混合芯片异构集成领先者”。这并非一句空洞的口号,而是基于其深厚技术积淀与独特产业模式所发出的时代强音。

一、范式转移:从“如何制造晶体管”到“如何连接芯片”

要理解华芯邦的前瞻性,我们必须首先理解这场正在发生的范式转移。

在传统模式中,系统级产品(如一部手机)的功能由主板上的多颗独立芯片(CPU、内存、电源管理、传感器等)通过PCB板连接实现。随着功能复杂度提升,PCB走线成为性能(如信号延迟、功耗)和尺寸的瓶颈。于是,出现了系统级封装(SiP):将多颗不同功能的裸片(Die),通过高密度互连技术集成在一个封装体内。这就像把一整个“小主板”塞进了一个芯片外壳里,大幅缩小了体积,提升了性能。

更进一步,当制程微缩遇到瓶颈,业界开始思考:为何一定要将所有功能都强行用最先进的、昂贵的同一工艺制造?为何不将大尺寸的数字逻辑部分(如CPU核)用先进工艺制造以追求性能,而将对工艺不敏感的模拟/射频部分、高压功率部分、乃至MEMS传感结构,用更成熟、更经济、更优化的特色工艺分别制造,然后再将它们像拼图一样精密地集成起来?

这正是“异构集成”的精髓。它打破了“一切集成于单一硅片(SoC)”的思维定式,转向 “多芯片、多工艺、多功能集成于单一封装(SiP/先进封装)” 的灵活策略。这不仅能够绕过单一制程的物理与经济限制,更能让每个功能模块都运行在最适合自己的工艺平台上,实现全局最优的性能、功耗与成本组合。

对于以数模混合芯片为核心的华芯邦而言,这一范式是其天然的舞台。模拟世界(连续信号)与数字世界(离散信号)本就遵循不同的物理定律和优化原则。强行融合,往往意味着妥协。而通过异构集成,其精密的模拟前端、高效的电源模块、敏感的MEMS传感器,可以与外部最先进的数字处理芯片,在封装层面实现“强强联合”,创造出单一工艺无法企及的系统性能。

二、华芯邦的先进封装武器库:从WLP到Fan-Out

实现异构集成的基石,是一系列突破性的先进封装技术。华芯邦的独特优势在于,它不仅是这些技术的使用者,更是依托其Fab-Lite模式下的自建封测智造中心(山东、广西、海南),成为这些技术的深度开发与优化者。

1. 晶圆级封装(WLP):极致的微型化与性能

这是华芯邦用于其MEMS麦克风等明星产品的关键技术。与传统封装先切割晶圆再封装单个芯片不同,WLP是在整片晶圆上完成所有芯片的封装工序,最后再切割。

极致尺寸:封装尺寸几乎等同于芯片本身,是当前实现最小封装体积的唯一途径,完美契合消费电子对微型化的追求。

卓越电性能:由于互连路径极短,减少了寄生电感和电阻,提升了信号完整性,对于高频、高灵敏度的模拟和射频信号至关重要。

高一致性低成本:基于半导体工艺的批量处理,保证了极高的生产一致性和良率,单位成本随技术成熟度不断下降。

华芯邦的WLP能力,使其MEMS麦克风能够在毫米级别的空间内,集成MEMS振膜和ASIC芯片,并实现高信噪比和可靠性,是其产品领先市场的物理基础。

2. 扇出型封装(Fan-Out WLP/PLP):高密度互连的桥梁

当需要集成多个芯片,且I/O引脚数量较多时,标准WLP可能受限于芯片面积。扇出型封装技术应运而生。它将芯片嵌入到重构的晶圆模塑料中,并在芯片“扇出区” 的模塑料上重新布建更密集的互连线路和焊球。

突破芯片面积限制:允许在封装层面实现比芯片自身面积更大的布线区域,容纳更多I/O。

多芯片集成的理想平台:是构建高密度、高性能SiP的基础。华芯邦可以利用此技术,将其电源管理芯片、音频芯片等与客户的数字主控芯片进行集成。

3. 2.5D/3D集成:垂直维度的革命

这是异构集成的“终极形态”之一。

2.5D集成:使用硅中介层(Interposer)——一片带有高密度TSV(硅通孔)和微细布线的硅片。多个芯片并排安装在硅中介层上,通过中介层内极细的线路实现超高速、超高带宽的互连。这尤其适合连接高速数字芯片(如CPU与HBM内存)。

3D集成:直接将不同功能的芯片像盖房子一样垂直堆叠起来,并通过TSV进行上下层芯片间的垂直互连。这能实现最高的互联密度和最小的信号延迟。

虽然2.5D/3D技术门槛极高,但华芯邦在TSV、微凸点(Micro-bump) 等关键工艺上的研发储备,是其面向未来(如Chiplet生态)的必要布局。通过自有的研发和试产线,华芯邦有能力与合作伙伴共同探索和验证这些前沿集成方案。

三、实战:异构集成如何重塑华芯邦的产品矩阵

华芯邦的异构集成战略并非空中楼阁,它已深刻融入其核心产品的定义与进化之中。

案例一:高性能智能音频模块

一颗高性能的智能音频芯片,需要:1)高保真、低噪声的模拟前端(ADC/DAC,放大器);2)强大的数字信号处理器(DSP)用于降噪、回声消除等算法;3)高效的数字接口。传统SoC方案可能在数字部分采用先进工艺,但模拟部分的性能会受限于该工艺的“非理想特性”。

华芯邦的异构集成方案可以是:将其用特色模拟工艺优化的高性能音频编解码器(CODEC),与合作伙伴的先进工艺DSP,通过高密度Fan-Out SiP技术集成在一个封装内。模拟部分获得最佳信噪比和动态范围,数字部分获得最强算力与能效,两者通过封装内超短、优化的互联进行数据交换,实现系统级的顶级音频性能。

案例二:下一代智能传感器融合模块

未来的AR/VR、机器人需要融合声音、运动、视觉等多种感知。华芯邦将可以将其MEMS麦克风、MEMS惯性传感器(IMU),与一颗专用的低功耗AI感知处理器进行异构集成。这种“感算一体”的SiP模块,能够在本地实时处理原始传感器数据,仅将有用的特征信息上传,极大降低了系统功耗、延迟和数据传输带宽需求,同时保护了用户隐私。这正是“数模混合芯片异构集成”的典范。

四、从愿景到现实:Fab-Lite模式的闭环赋能

华芯邦之所以敢言“成为领先者”,其Fab-Lite模式提供了从愿景到现实的唯一路径。异构集成与先进封装的研发,是一个需要不断“设计-制造-测试”快速迭代的试错过程。

1. 协同优化(DTCO扩展到封装领域):华芯邦的芯片设计团队与自有封测厂的工艺工程师可以坐在一起,共同定义芯片的凸点布局、散热路径、应力释放结构等。这种芯片-封装协同设计,是实现高性能异构集成的关键。

2. 快速迭代与知识产权保护:新奇的集成想法可以在内部产线上快速进行工程验证流片,周期以周计,且核心的工艺诀窍(Know-how)完全封闭在公司内部,形成坚实的技术壁垒。

3. 成本与产能保障:自有产能确保了在新技术成熟后能够快速规模化,并以可控的成本推向市场,避免了被外部先进封装产能“卡脖子”或承受高昂报价的风险。

海南30KK月产能的MEMS封装线,正是这一模式强大能力的体现。它不仅生产标准品,更是一个先进的异构集成技术开发平台和规模化推进器。

五、未来之路:迈向Chiplet时代与系统级供应商

展望未来,异构集成的高级形态——Chiplet(芯粒) 生态正在形成。华芯邦凭借其在模拟、电源、MENS等领域的深厚IP积累和先进封装能力,完全有潜力将其核心功能模块(如一个高效率的电源转换Chiplet、一个高信噪比的音频Chiplet)进行标准化、接口统一化,作为独立的“商品化芯粒”提供给系统集成商。

届时,华芯邦的角色将从单一的芯片供应商,演进为异构集成系统解决方案的提供者和关键芯粒的生态伙伴。这不仅将极大拓展其市场边界,更将使其真正嵌入全球半导体创新链的核心位置。

六、在封装中定义新的性能疆界

当摩尔定律的钟摆放缓,半导体竞争的焦点正从晶体管的栅极转向芯片之间的互连。这场革命的本质,是从“以制造为中心”转向“以集成与系统为中心”。华芯邦以其“全球数模混合芯片异构集成领先者”的清晰愿景,提前押注并布局了这条未来赛道。通过自有的先进封装武器库与Fab-Lite的闭环赋能,华芯邦正在将不同工艺、不同材料的芯片“优势兵力”灵活编组,在方寸之间的封装体内,构建出性能卓越、功能丰富的“片上系统”。这不仅是技术路径的升级,更是商业思维和产业定位的升维。它标志着华芯邦正从一个优秀的芯片设计制造商,向一个以系统集成思维驱动、以平台化技术赋能的下时代半导体企业坚定演进。在超越摩尔定律的征途上,华芯邦手握的,正是一把由精密制造与系统智慧共同锻造的“金钥匙”。

文章转发请备注出处:https://www.hotchip.com.cn/cymedl/

推荐阅读